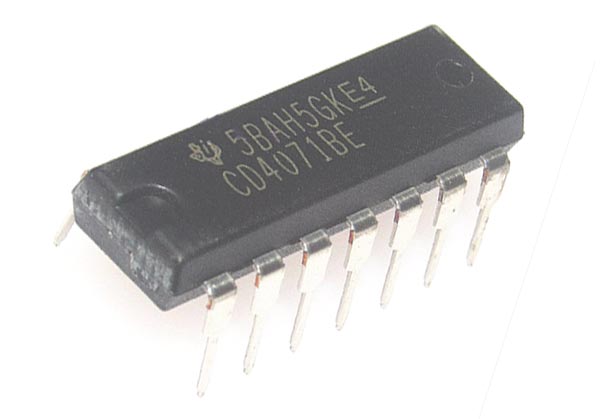

CD4071 OR gate

484 in stock

Quick Overview:

- Dual Input OR Gate – Quad Package

- Typical Operating Voltage: 5V

- Operating Voltage Range: -0.5V to +20V

- DC input current: ±10mA

5.00 SAR

484 in stock

The CD4071 is a Dual Input OR Gate with Quad package. Meaning it has four OR gate IC inside it, each of which can be utilized independently. OR gates are used in building Logic level circuits like Encoder, Decoder multiplexers etc. Logic level gates like CD4071 and flip-flops play a vital role in digital electronics.

If you are looking for an IC to perform logic level OR operation with two inputs, then this IC might be the right choice for you. If you have more than two inputs for your OR gate then you should look into three input and four input OR gates.

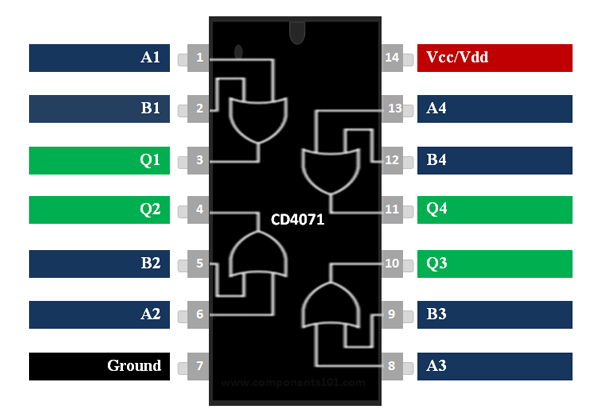

Pin Name

Description

1,6,10,15

OR Gate Input pin (A)

First Input pin for the OR gate

2,5,11,14

OR Gate Input pin (B)

Second Input pin for the OR gate

3,4,12,13

OR Gate Output pin (Q)

Output pin for the OR gate

7

Ground

Connect to the ground of the circuit.

14

Vcc (Vdd)

Used to power the IC. Typically +5V is used

Features:

- Dual Input OR Gate – Quad Package

- Typical Operating Voltage: 5V

- Operating Voltage Range: -0.5V to +20V

- DC input current: ±10mA

- Power Dissipation: 500mW

- Minimum logic Low voltage @+5V: 1.5V

- Minimum Logic High voltage @+5V: 3.5V

- Propagation Delay @5V : 250ns (maximum)

- Transition Time @5V :200ns (maximum)

- Available in 14-pin PDIP, GDIP, PDSO packages

Note: Complete Technical Details can be found at the CD4071 datasheet provided below this article.

Salih Musa (verified owner) –

السعر معقول و جودة المنتج ممتازة

Salih Musa –